CXL 2.0将实现内存池技术,这听起来很棒,但具体容量有多大还有点模糊。内存池能容纳多少数据呢?目前还没有确切的答案,但我们可以试着估算一下。1PB 听起来怎么样?甚至更多?

潜在的内存池容量取决于提供它的服务器。这又取决于服务器的CPU和PCIe通道支持以及DRAM DIMM模块的容量。我们从Sapphire Rapids处理器开始,并在计算过程中得到了MemVerge的专家Beau Beauchamp和Objective Analysis的Jim Handy的帮助。

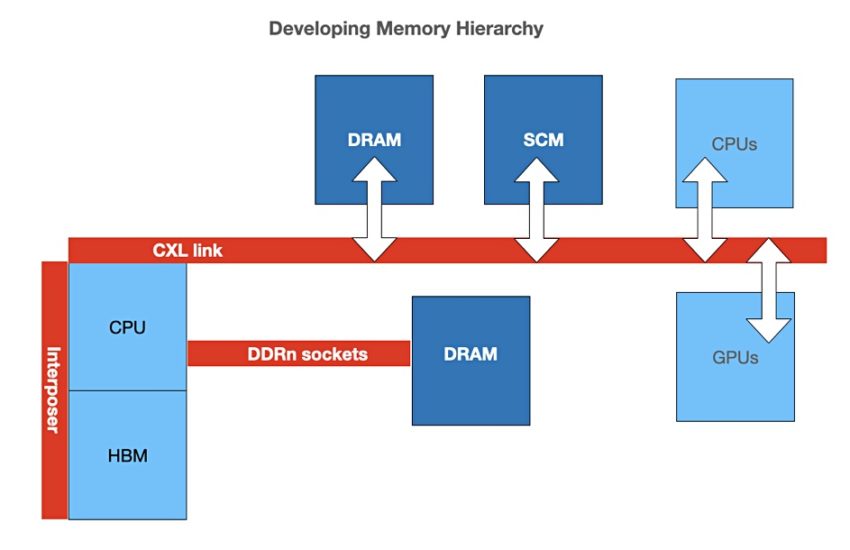

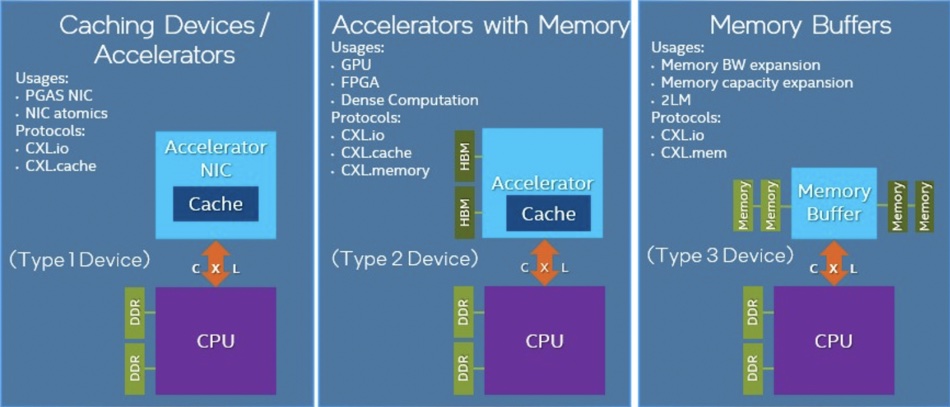

CXL 2.0在服务器CPU主机和三种设备类型之间维持缓存一致性。

- 第一类型设备是具有缓存的I/O加速器,例如智能网卡,它们使用CXL.io和CXL.cache协议与主机处理器的DDR内存通信。

- 第二类型设备是带有自己的DDR或HBM(高带宽)内存的加速器,它们使用CXL.io、CXL.cache和CXL.memory协议与主机共享内存,并将加速器内存与主机共享。

- 第三类型设备仅为内存扩展缓冲区或池,并使用CXL.io和CXL.memory协议与主机通信。

类型三设备将通过链路连接到服务器主机,最初使用PCIe 5.0。后续版本将使用PCIe的6和7等版本。英特尔即将发布的第四代Xeon SP Sapphire Rapids CPU将支持CXL 1.1和2.0。

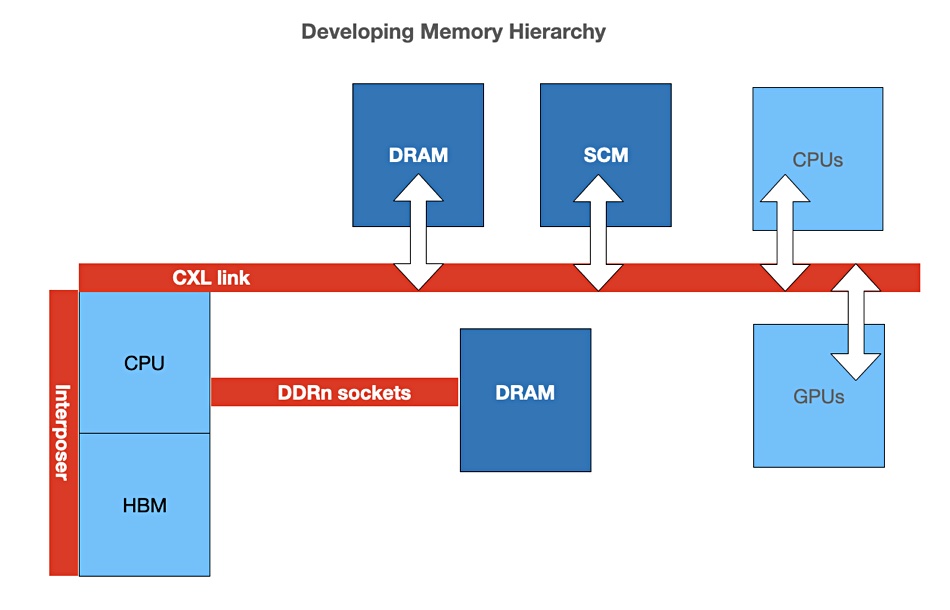

该处理器将具有高达56个核心,8个DDR5 DRAM插槽,支持64GB的HBM2e,每个组件平铺支持16GB,并具备高达128个PCIe 5通道,以及Optane PMem 300设备。

Beauchamp的观点

Beauchamp告诉我们:“Sapphire Rapids支持8个DIMM插槽,因此可以使用512GB的DIMM进行配置,最多可达4TB,但这样做的经济性将使其成为一种罕见的情况。”

CXL 2.0将支持16个PCIe通道。Beauchamp提供了更多细节:“CXL支持每个链路上1到16个通道,以2的幂次方递增。每个PCIe 5通道提供4GB/sec的带宽,因此x16链路提供128GB/sec的带宽。DDR5通道的带宽约为38GB/sec,因此如果直接连接CXL内存模块,x4的CXL链路(32GB/sec)是更可比的选择。整个行业普遍倾向于使用x4链路的CXL内存卡。”

他进一步计算了这意味着多少个DDR通道。“支持多个CXL链路。我确信Sapphire Rapids拥有很多个PCIe通道(接近100个),我假设其中三分之一到一半可以用于CXL,所以我们假设有三个x16组(每个组可以像PCIe一样分为四个x4链路),这相当于大约多了12个DDR通道。我不知道机箱设计将包含多少个插槽。”

使用最大的512GB DIMM容量,“多了12个DDR通道”意味着每个Sapphire Rapids CPU理论上可以拥有6TB的CXL DRAM容量,这可以添加到其本地直连的4TB DRAM上,总共达到10TB。

Beauchamp说:“CXL 2.0支持切换,因此使用x16链路连接到一个切换扩展多插槽(超过10个插槽)的内存盒是可以想象的。多个服务器共享(划分)50至60个插槽也是可以想象的。”

在此基础上更进一步

现在让我们加入MemVerge的内存机器技术。这是一种系统软件,将多台服务器的内存聚合到一个单一的池中。在2019年4月,我们了解到它可以支持一个由128台服务器设备组成的集群,每台设备具有512GB的DRAM和6TB的Optane。

这意味着从理论上讲,我们可以将单个Sapphire Rapids服务器的最大6TB DRAM聚合在一起,形成一个768TB的内存池,再加上服务器中聚合的128个x4TB = 512TB的本地内存,总计1.28PB。

Beauchamp表示,在短期内可能会有一些技术问题阻碍这种内存池化的愿景。首先:“以前的Xeon处理器每个插槽都有一个最大的内存限制(即,可以成为‘主’一致性代理的内存)。Cascade Lake有多个不同的SKU(1TB、2TB和4TB)。Ice Lake只有一个SKU,即4TB。我不知道Sapphire Rapids在这方面会采取什么措施,但我预计它会增加,可能是增加到8TB,甚至可能达到双倍?这个限制可能会影响你每个插槽达到10TB的结果。”

第二:“CXL 2.0的交换机配置有限,因此在128台服务器之间实现完全灵活的共享可能并不实际。(CXL 3.0的目标是更强大和简化的交换)。”

Handy的观点

对于“可能有多少CXL内存?”的问题,Handy表示:“我认为答案将来自另一个方向。”

系统的内存空间将受到多种因素的限制,不仅仅是你提到的因素。近端内存(实际与CPU接触的内存)受到电容负载和CPU引脚驱动的芯片数量的限制,甚至受到DRAM引脚驱动的芯片数量的限制。特定芯片的内存密度在这里非常重要,并且随着时间的推移会增加。

对于远端内存(通过控制器与CPU通信的内存,即CXL或OpenCAPI),可以连接的内存芯片数量几乎没有限制,因此其它因素决定了可以连接的内存大小。(据我了解,CXL中提供了大量的内存地址,尽管我一直在努力找到确切的答案。我查阅了628页的CXL 2.0规范,并打了几个电话,但尚未得到确切的答案。)

那些‘其它因素’将决定最大的内存容量?我能想到的两个因素是CPU和缓存控制器支持的物理地址长度,通常它们是相同的。CXL使用非对称一致性,这意味着单个CPU管理整个系统的一致性。CPU上的任何限制都将决定可以管理的最大内存大小。如果Sapphire Rapids与其前身相似,它将以多种版本提供,具备各种寻址能力。

“…因此你得不到一个确切的答案!”

然后Handy提出了一些详细观点:

- 可以连接到Sapphire Rapids芯片的最大DDR DRAM受CPU芯片的地址引脚限制,而不是受其使用的DRAM芯片的限制。三星利用这一点制造了具有堆叠DRAM芯片的超大DIMM(128GB、256GB和512GB),使用了为HBM开发的TSV技术,并以高价出售它们,所以你的计算(1.28PB)必然是不准确的。随着更密集的DRAM的出现,这也会造成不准确性。三星也可能选择在其堆叠中加倍DRAM芯片的数量,这也会引起不准确性。

- HBM的支持也取决于寻址。我预计英特尔会将地址位数设得稍高,以便允许未来设计者使用五年后DRAM制造商可以供应的任何DRAM。

- 每个CXL通道是单个通道。该通道可以使用PCIe或CXL进行通信。这是在启动时确定的。我认为CPU芯片上的PCIe通道数可以从零增加到无限大,而16是目前的实际数目。

- 单个CXL通道上的DRAM容量应该比您的512GB估计值大得多。这意味着内存量受CPU的地址范围限制。

“这并不是一个简单的答案,但CXL被设计为拥有长寿命,并且这涉及提供过多(目前至少如此)的地址范围。”

这带来的结果是,我们计算的1.28PB的近端内存加上远端内存的总量可能太小了,但没有人知道确切的答案。这取决于CPU的DRAM容量、CPU的PCIe通道数、CXL交换机容量和CXL内存模块容量——这是四个不确定性的领域,可能还有更多。

Eideticom首席技术官Stephen Bates提出:“你可能会遇到供电和散热所有那些内存的问题,但这只是一个物理问题。”

超大规模云服务商和大规模内存

我们计算的1.28PB内存量是一个理论值,正如Beauchamp所暗示的那样,从经济角度来看,这是不太可能的。但是想象一下一个超大规模的公有云服务商这样做——为一组Sapphire Rapids服务器提供一个大规模的内存池,并通过组合性软件实现为超大规模内存数据库/数据仓库应用程序提供100TB到1000TB的内存实例,这些实例将以当前难以想象的速度运行。可以添加Optane存储级内存作为持久存储,例如检查点。

客户可以在人工智能、机器学习和分析应用领域使用这个设施进行突发处理。

我们正在考虑各种可能性,但是凭借Sapphire Rapids和CXL 2的基础,它们非常接近。它们代表了内存数据集部署和使用它们的应用程序执行速度的潜在巨大增长。

备注:Xeon Ice Lake处理器具有46位物理地址空间为 64TB。