业界正迅速向2022年的PCIe Gen5时代迈进,因此,我们开始看到许多公司发布有关PCIe Gen5和CXL产品的公告。Astera Labs为该行业提供了新的Retimer系列产品,该公司还宣布了其EQUINOX产品,这是一张PCIe Gen5的Retimer add-in card,PCIe Gen3 Retimer存在差不多已经10年了,可是我们可能还没有看到许多PCIe Gen3的retimer,随着我们快速地过渡到PCIe Gen4,然后PCIe Gen5,再然后PCIe Gen6,retimer将变得更普遍。

Astera Labs Aries Compute Express Link Retimers

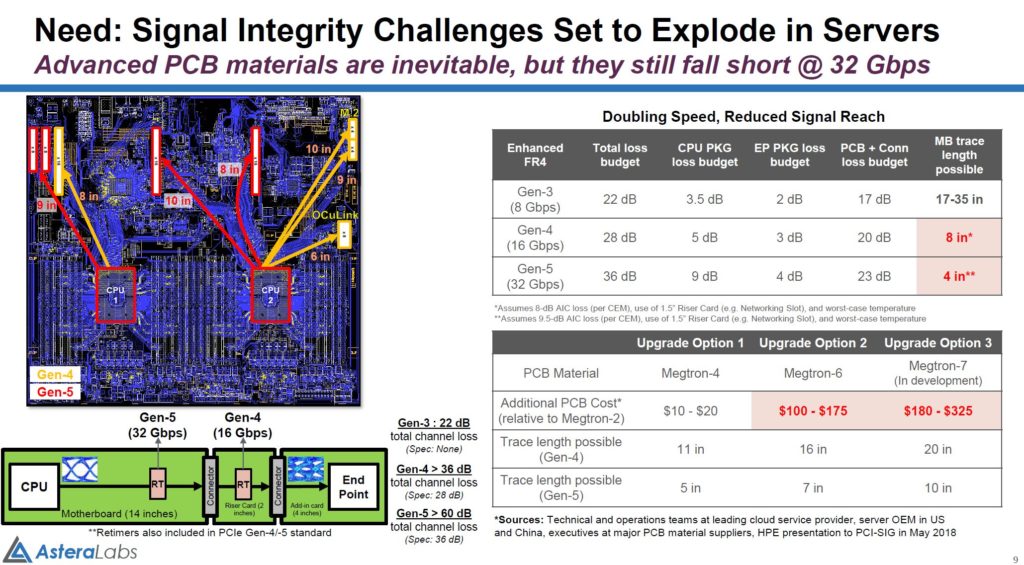

向不了解Retimer的读者介绍一下,Retimer是现代设备中常用的芯片,有助于扩展I/O的传输距离,许多人都熟悉在服务器和存储系统的设备上经常使用Retimer,因为这些Retimer常常增强NVMe SSD的traces信号。随着我们转向PCIe Gen4和Gen5,PCIe信号通过PCB的传输距离开始下降,使我们不得不想别的方法来增强PCIe信号来延长传输距离。

除了PCB走线的长度,增加诸如连接器之类的组件进一步缩短了传统的直线PCB布线的实际达到的范围,这儿的关键是供应商将不得不为主板选择使用更好的PCB材料,使用更多的线缆和/或使用Retimer和PCIe交换机。

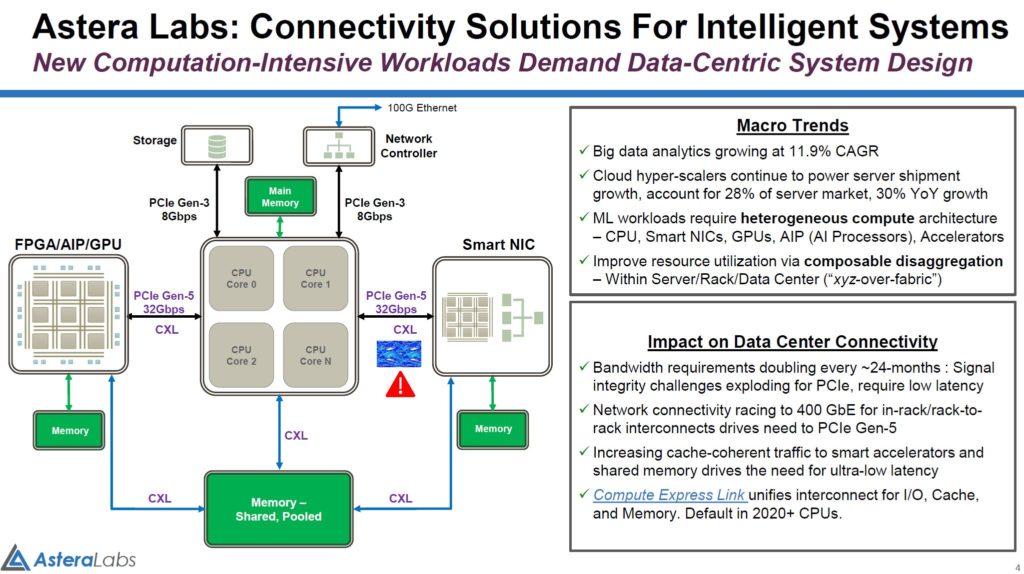

有了PCIe Gen5和CXL,我们有足够的带宽来实现新的拓扑结构,例如可在CPU,GPU,FPGA,DPU和其他组件之间使用的共享的内存池,这样做可以节省大量成本,并将革命性地改变服务器的架构形式。

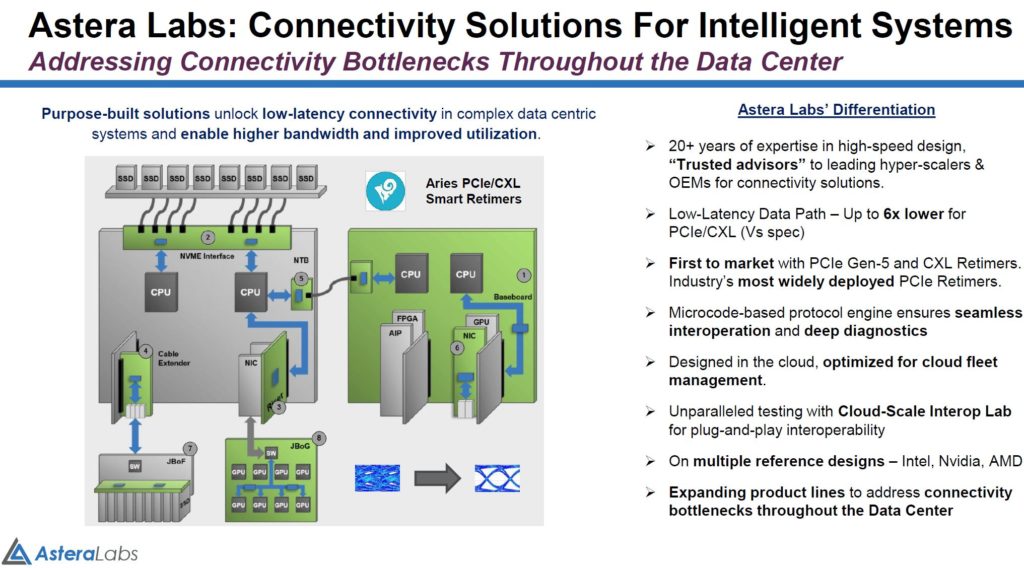

Astera Labs解决方案的一部分是为PCIe Gen5/CXL提供低延迟的Retimer芯片(PT5161LX,PT5081LX)。该公司正在与Intel(英特尔)针对即将推出的Sapphire Rapids芯片以及NVIDIA,AMD等一起进行下一代芯片的设计。低延迟对于Retimer芯片的重要性不可低估,尤其是当电路中可能存在多个Retimer的情况下。

CXL规范相对会宽松一些,因此我们看到Astera Labs和诸如Microchip的公司宣布他们正在与Intel紧密合作。

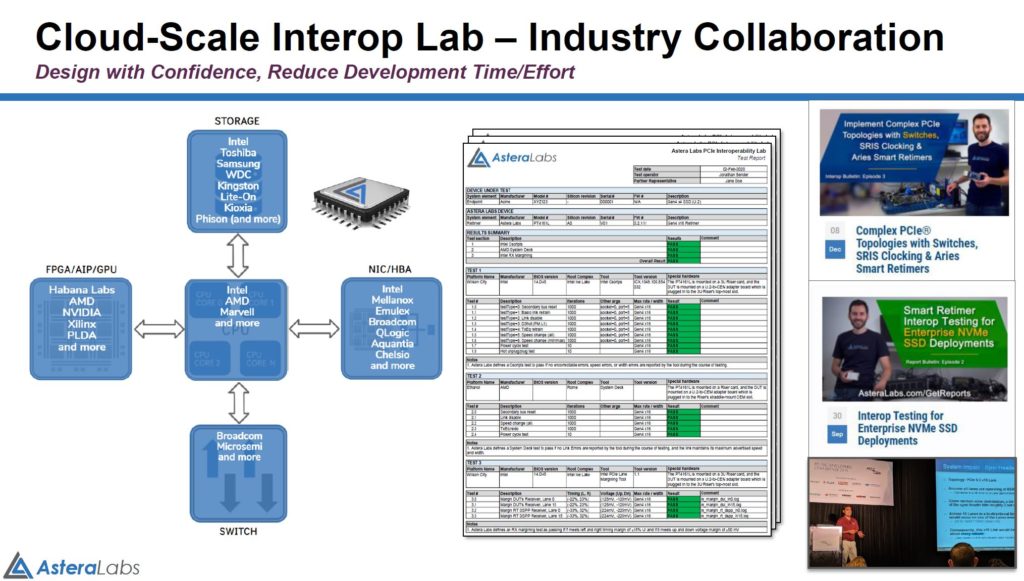

该公司还拥有自己的互操作实验室,正在与许多合作伙伴合作,以确保下一代PCIe Gen5/CXL设备能够可靠地开机。随着我们从老化的PCIe Gen3进入更快速的开发周期,确保产品快速上市将变得更加重要。

Astera Labs与众不同的部分在于它具有内置控制器,因此可以将遥测数据馈送到云提供商的系统,以确保链接能正常工作。该公司表示,由于它内置控制器,因此甚至可以通过固件更新解决一些潜在的问题。

小结

总体而言,这似乎只是一个小小的一步,但是下一代系统(或者说是下下代,考虑到我们已经在迭代周期中)将使用比PCIe Gen5时代所看到的更多的Retimer。系统将继续变得越来越大,越来越复杂,这意味着诸如PCIe trace长度之类的基本问题的解决方案将变得更加明确。

同时,很难离开这里,感觉这就像是Astera Labs的终结游戏,整个CXL生态系统将需要更多基础架构,例如交换机,内存控制器,以及更多将从提供端到端连接解决方案中受益的基础架构。