在2019年4月,我们曾爆料了为何AMD EPYC Rome 2P服务器将具有128-160 PCIe Gen4通道。在2020年,Dell EMC和AMD展示了EPYC的灵活性,这在英特尔至强服务器甚至在即将到来的2020/2021 Ice Lake新一代中也只能是幻想。 在本文中,我们将向你展示Dell EMC PowerEdge R7525如何启用160x PCIe通道来连接设备,同时保持比我们在Intel Xeon系统上看到的更大的灵活性。这是我们18个月以来一直希望做的文章,因此,我们很高兴向你展示Dell EMC对AMD技术的设计和实现,并讨论为什么这是服务器的未来。

AMD EPYC 7002 “罗马” 双Socket工作原理

我们可以一直回顾到AMD EPYC 7001系列的“Naples”那一代,在那一代中,有四个die,每个die都具有I/O和计算资源。针对单Socket的配置,每个die都有32条lane可以被配置成PCIe lane。在双Socket配置中,每个die需要使用其中的十六个lane来连接到第二个socket上的对应lane。

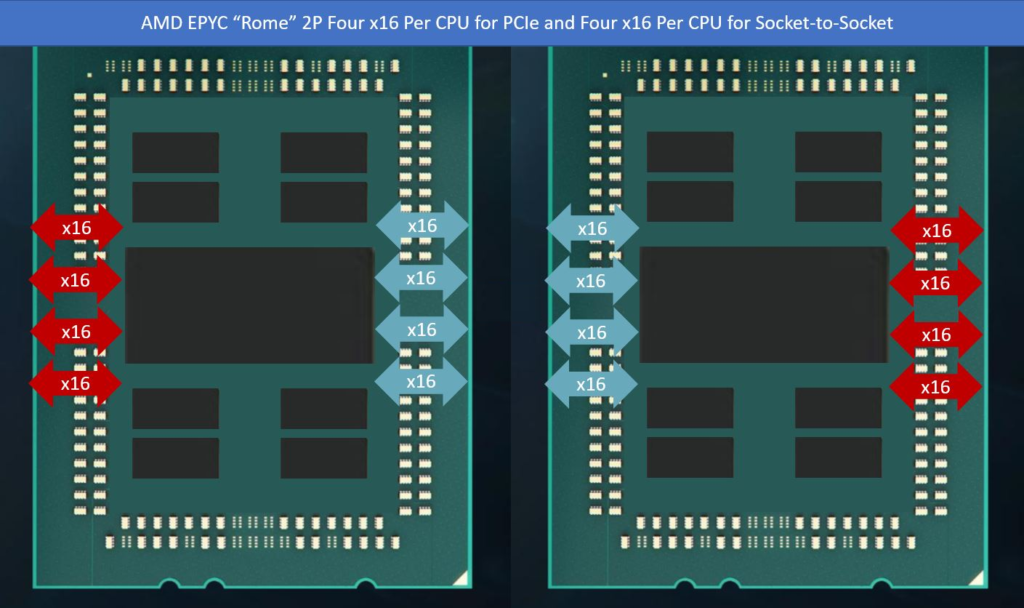

AMD EPYC 7002罗马系列处理器进行了一个根本性而且重要的变化,随着AMD EPYC 7002 I/O die的推出,x86的内核及其缓存现在与具有外部I/O的I/O die已经分离开了。在新一代产品中,仍然可以使用具有16个lane的全部8个块作为PCIe Gen4的lane。在双Socket配置中,为了与Naples EPYC 7001系列匹配,每个CPU使用这些x16块中的四组来进行Socket到Socket的互联。

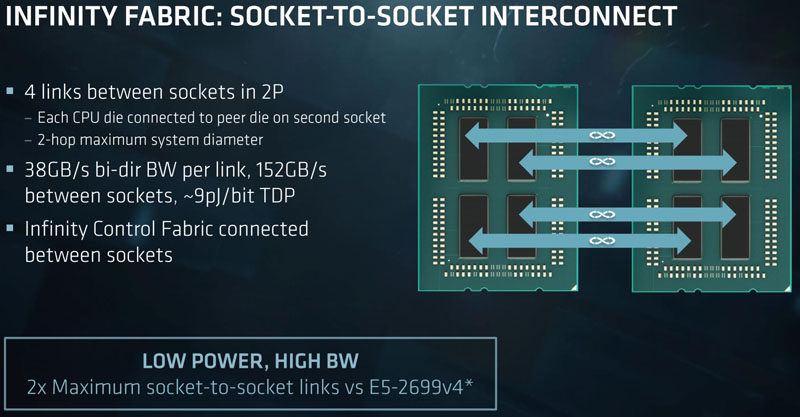

接下来,一些魔幻的事情就发生了,这些链接的数量可能是一样的,但速度却与AMD EPYC 7001系列的”Naples”系统是不一样的。请记住,AMD的Infinity Fabric使用与PCIe相同的I/O,这就是我们获得双重身份的方式。由于EPYC 7002系列的CPU已经从PCIe Gen3迁移到Gen4,因此链接速度需要加倍。所以,Rome的Infinity Fabric不仅存在于I/O Die中的单个silicon里,而且还受益于更快的链接速度。

AMD在其PCIe Gen3 Naples一代产品上与英特尔UPI的CPU Socket互连相比就已经具有竞争优势了,而AMD的Rome实际上具有上一代产品2倍的性能。对于Intel的CPU,Intel倾向于每代增加10%左右的性能,因此这对于AMD来说是一个巨大的跳跃。我们还看到英特尔在其第二代英特尔®至强®可扩展的升级中削减了Socket到Socket的带宽。正如我们在“英特尔至强金牌6258R评估”中发现的那样,需要注意的是,在运行在Platinum 8280上的虚拟化工作负载中,丢失了三分之一的Socket到Socket的带宽,但这远没有价格差异的影响那样大。 实际上,AMD的带宽增加了一倍,而英特尔在许多方面都将双Socket系统在Socket到Socket的带宽上减少了33%。

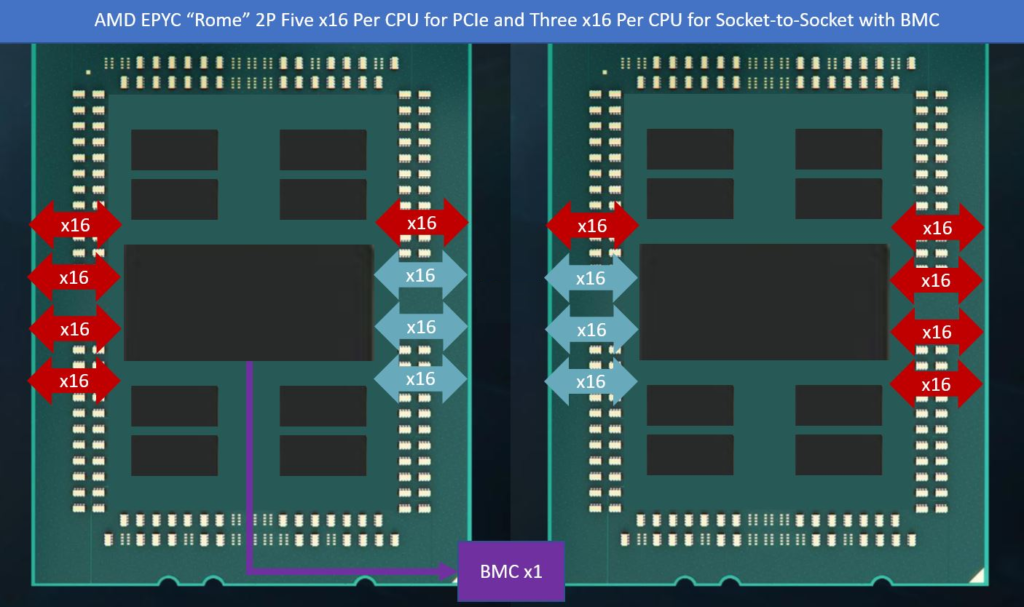

AMD及其合作伙伴很早就意识到了这一点,并提供了一个有趣的解决方案。由于AMD具有更具跨人性的Socket到Socket的Infinity Fabric/PCIe系统,因此你可以将其中一些lane用作PCIe Gen4 lane,而不是将它们用作socket到socket的link。在下图中,我们描述了这种情况。

这总共产生了总共160x PCIe lane,相比Naples那一代,还提供了大概50%左右的socket到socket的Infinity Fabric带宽。对于那些想知道的人,我们已经看到了192x PCIe Gen4 lane的设计,但据我所知,160x PCIe通道是AMD官方支持的。

到目前为止,我们看到的大多数设计都是使用128或160个PCIe lane。但是,Dell EMC有办法可以兼顾两者并具有更大的灵活性。

Dell EMC PowerEdge R7525 160X PCIe Gen4 Lane的配置和灵活性

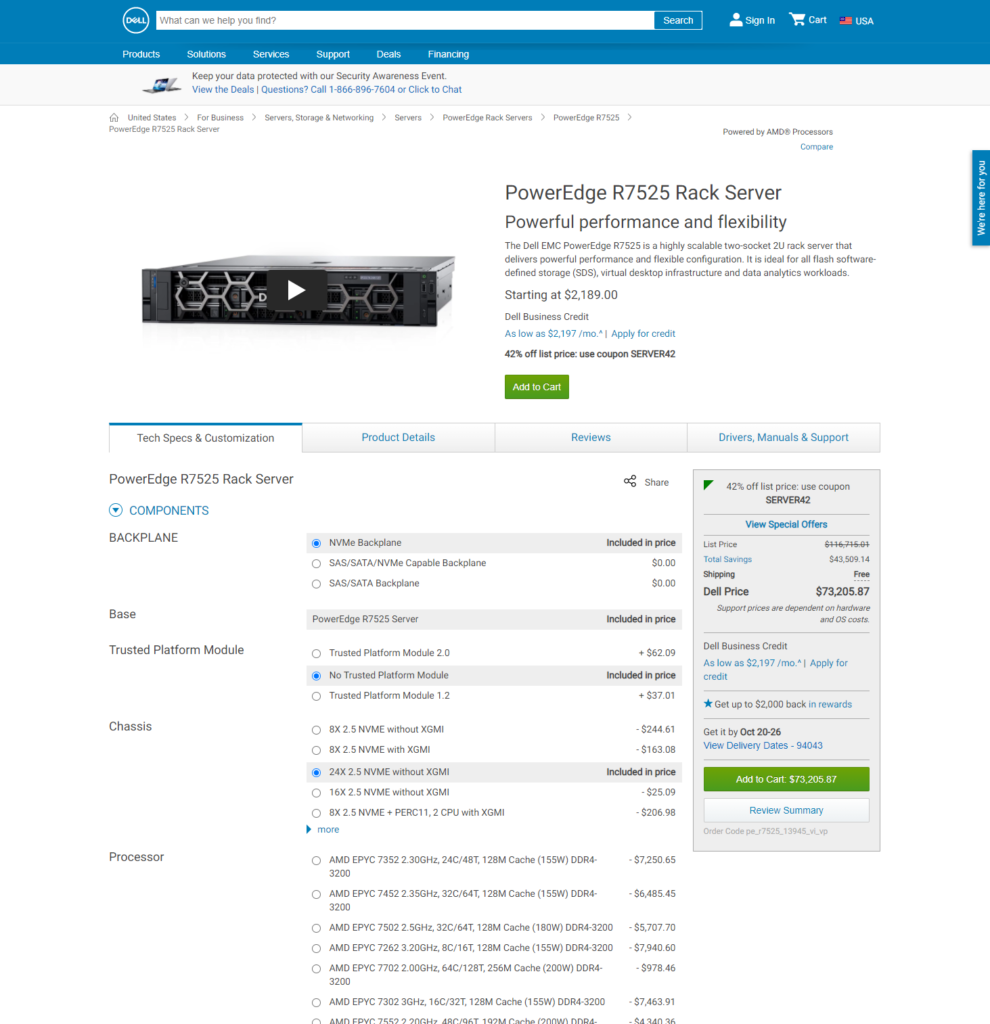

Dell EMC PowerEdge R7525是Dell的双Socket AMD EPYC 7002(可能还有EPYC 7003 “Milan”)的平台,它支持具有PCIe Gen4以及大量灵活性的当前最先进的AMD EPYC。在进行对系统进行查看时,我们意识到我们有太多可用的PCIe Gen4 lane,让我们来算一算。

首先,我们将从Riser开始,我们有两个PCIe Gen4 x16和两个x8的电气插槽,这总共就有48个PCIe Gen4 lane了,顺便说一句,由于这些是PCIe Gen4的,不是PCIe Gen3,它们提供了整个当前双Socket Intel Xeon可扩展系统的有效带宽,当然,我们完全期望还有更多。

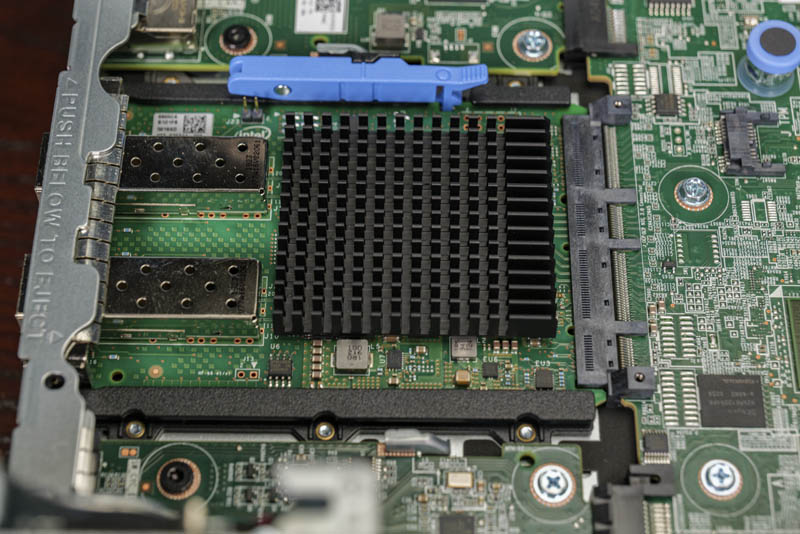

在Riser下面,我们有一个OCP NIC 3.0,在这里,我们有一个基于Intel X710的双SFP+ 10Gbs NIC,但是,这些插槽是为PCIe Gen4设计的,最多支持x16电气信号,因此它们最多可以处理双100Gbps端口的NIC。将来,这可以作为Project Monterey的一部分来运行VMware ESXi,从而允许控制/管理和应用程序平面分解。加上这儿的16个lane,我们总共有64个lane,这和Ice Lake Xeon处理器的价值相当。

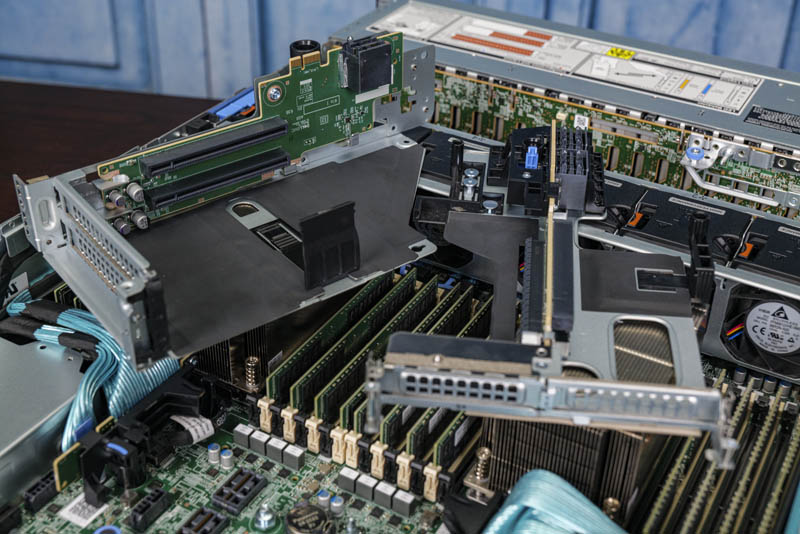

然后事情变得有些疯狂了,在系统的前面板,我们有24个NVMe SSD,每个SSD具有PCIe x4连接。24个驱动器(带4个通道)每个盘有4个lane,总共需要96个lane。我们仔细检查了系统,这些盘没有PCIe switch,它们都是通过线缆直接连接的。

下面是24个NVMe设备中96个PCIe lane以及OCP NIC的拓扑图。

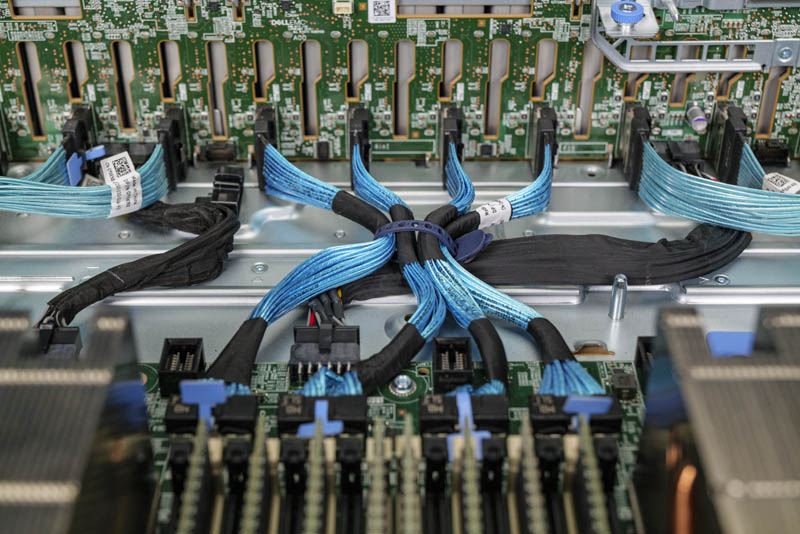

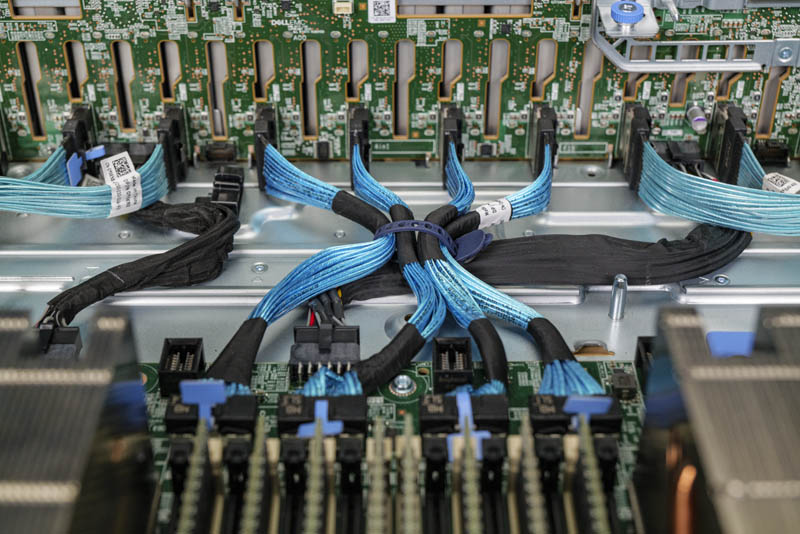

Dell如何做到这一点实际上是一个聪明的工程设计,我们移除了PowerEdge R7525的风扇以获得更好的视角。可以看到,系统中间有四根线缆,每根线缆连接两个NVMe SSD盘,具有8个PCIe lane,这四根线缆为我们提供了三分之一的连接性,或者为我们提供了系统前面板上的24个NVMe SSD中的8个。

当我们查看Dell配置选项上的24-bay选项时,我们看到它说”without XGMI”。对于高层翻译,在这种情况下将XGMI(或xGMI)视为等同于Infinity Fabric link。

当我们再次查看线缆时,可以看到线缆非常靠近CPU,比PowerEdge R7525主板上的其他PCIe Gen4 riser和电缆接头更近。

通过阅读服务手册,我们发现可以将它们连接起来以提供CPU到CPU的连接,或者,正如我们在测试系统中看到的那样,它们可以用来将PCIe lane连接到机箱中的其他位置。这样的设计在简单性和灵活性上都非常出色。Dell不必进行多个不同的主板Gerber,而是采用了我们在上图中从淡青色变为红色的一对x16链接,并使其成为可配置的选项。

总结

除了PowerEdge R7525本身,它还演示了使用这些高速lanes作为CPU到CPU或PCIe互连的灵活性。英特尔如果要想让AMD EPYC 7002的竞争对手Cascade Lake Xeon达到同样效果,将会非常困难,因为它使用了专用的UPI和PCIe link的IP块,也许可以使用线缆UPI,但这不是一个简单的BIOS翻转能将其转变成PCIe的。

另一个方面,它向我们展示了服务器的未来是主板改变多少,在PowerEdge上,我们演示了主板上没有传统的PCIe x8或x16连接器。相反,它具有一个OCP NIC 3.0连接器,然后是用于Riser的高密度连接器,以及用于NVMe盘的线缆。例如,这些线缆可以将PCIe通道从前面板NVMe存储连接到Riser。由于PCIe Gen4,AMD EPYC Rome主板需要更多的PCB层和更高质量的PCB材质以确保信号完整性,但是仍然存在一些限制。随着我们进入到PCIe Gen4和PCIe Gen5时代,使用连接到设备的线缆来构建更多的模块化系统是一种更具扩展性和灵活性的模式。由于我们不能简单地依赖较长的PCB走线,因此我们正迅速进入一个系统会拥有比上一代产品更多电缆的时代。