在未来的几年里,随着内存、存储和加速器逐渐迁移到独立的机箱,服务器的形态有望经历深刻的演变。一项被冠以CXL的互连技术正推动着这场变革。

这一技术的升级规范,即版本3.1,于本周正式宣布。这次渐进性的更新不仅提供了更为迅捷、更为安全的计算环境,同时也为将数据中心打造成规模宏大的服务器奠定了更加牢固的技术基础。

新规范将支持目前仍在研发中的DDR6内存。作为DDR标准的制定组织,JEDEC对DDR6并没有进行详细的讨论。

目前,Intel和AMD的服务器芯片已经支持DDR5,尚未明确芯片组是否会支持DDR6。绝大多数硬件和云服务商纷纷支持CXL。

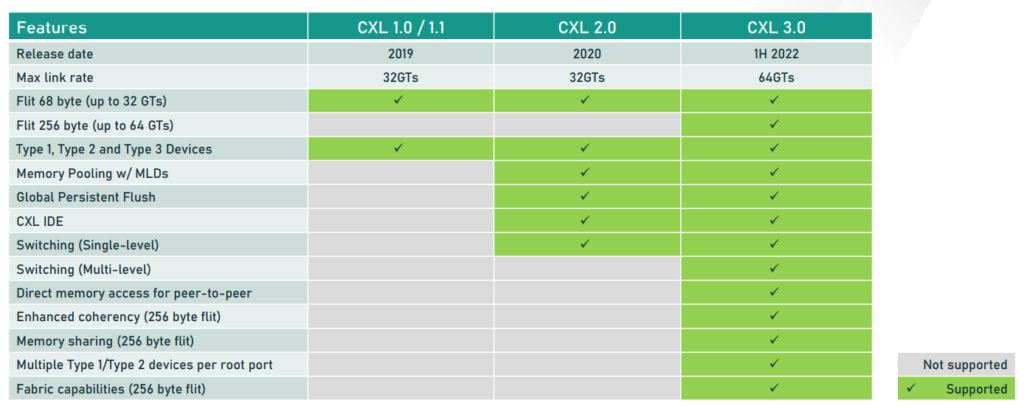

CXL 3.1是对CXL 3.0的一次渐进性改进,而后者则于一年多以前推出。作为系统中芯片、内存和存储之间关键的通信链路,CXL协议发挥着至关重要的作用。

CXL 3.0规范建立在PCIe 6.0的基础之上,拥有64GT/s的数据传输速度。相较于其前身CXL 2.0,后者基于PCIe 5.0,CXL 3.0的传输速度提升了两倍,正在逐渐在服务器系统中得到应用。

随着人工智能等技术的广泛应用,CXL已成为芯片组不可或缺的组成部分。机器学习应用对大量内存和带宽的需求日益增长,而CXL则允许在服务器之间进行存储和内存的集成。

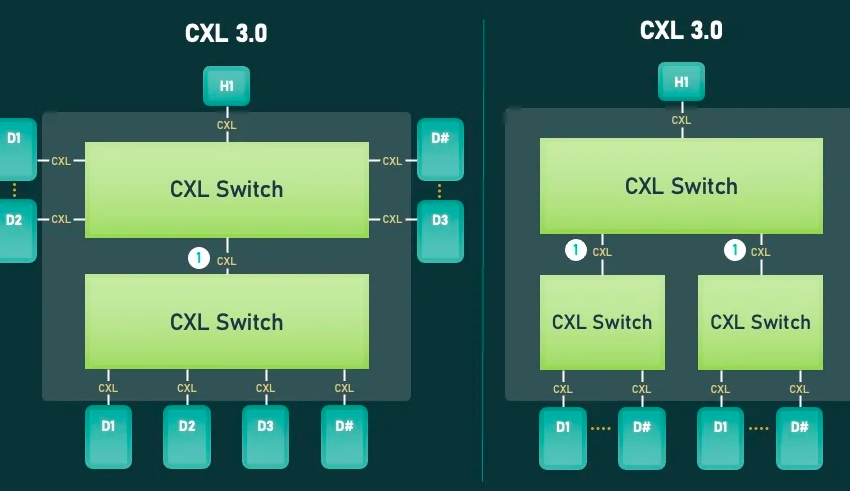

CXL 3.1协议具备开启更多对等通信通道的能力,实现了对内存和存储的独立分离,形成独立的模块。尽管通过传统网络和互连技术进行的分离已经讨论了十年,但CXL提供了实现广泛的计算资源可用性所需的可扩展性。

首先,CXL 3.1规范提供了支持新类型内存的途径,同时还能更加高效地将数据重新路由到内存和加速器。

一个重要的进展是关于在一个全局地址下集中内存资源的技术。这一功能被称为全局集成内存,对于建立内存与其它资源之间更快速连接至关重要。

加速器还将能够直接与内存资源实现高效通信。基于端口的路由的新功能有助于更迅速地获取内存资源。

CXL 3.1进一步支持在安全环境中执行数据的需求。这项技术的引入旨在促进保密计算,在Intel的Sapphire Rapids中已经引入了TDX指令,并在AMD的芯片中以SNP-SEV功能的形式存在。

新的规范明确定义了一套安全协议,以加强数据在内存、处理器和存储之间传输时的安全性。

该协议将检测需要身份验证的连接,以便在访问代码或信息的环境中打开硬件保险库。这些信息可能存储在处理器、内存或存储器上。Intel、Microsoft和其他公司采用多种验证方法,用于验证试图在受保护环境中访问数据的连接。