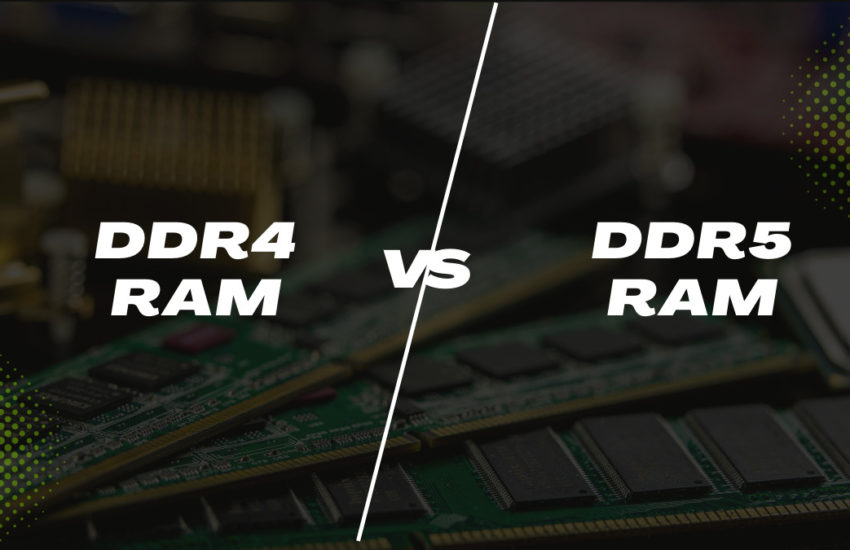

2021 年,JEDEC 宣布发布 JESD79-5 DDR5 SDRAM 标准,标志着行业向 DDR5 dual-inline memory modules (DIMM) 的过渡。DDR5 内存带来了许多关键的性能提升,以及新的设计挑战。计算系统架构师、设计人员和购买人员都想知道 DDR5 与 DDR4 有什么新功能,以及他们如何充分利用新一代内存。

DDR5 与 DDR4 DRAM 有什么变化

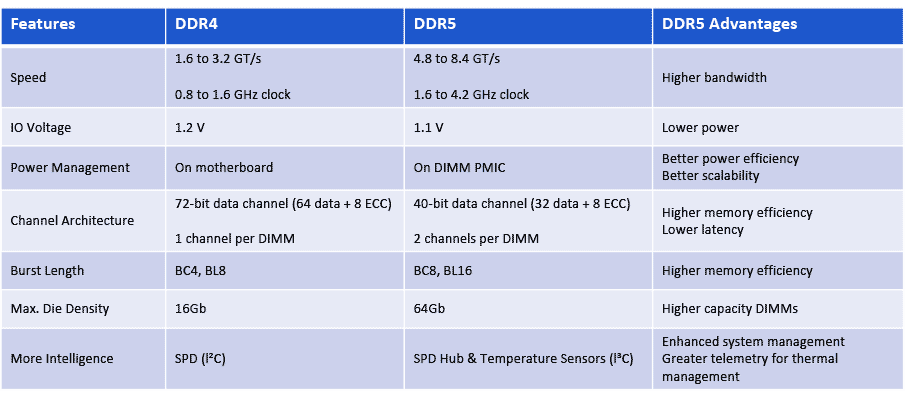

从 DDR4 到 DDR5 DIMM 过渡中的七个最重要的技术指标改进如下表 1 所示。

1. DDR5 可扩展至 8.4 GT/s

您永远无法拥有“足够”的内存带宽,而 DDR5 有助于满足对速度的永不满足的需求。DDR4 DIMM 在 1.6 GHz 的时钟速率下最高可达 3.2 千兆传输/秒 (GT/s),而初始 DDR5 DIMM 的带宽增加了 50%,达到 4.8 GT/s。DDR5 中集成了决策反馈均衡 (DFE) 等新功能,可实现更高的 IO 速度和数据速率。

2. 较低的电压使电源保持在可控范围内

第二个主要变化是工作电压 (VDD) 的降低,这有助于抵消以更高速度运行带来的功耗增加。使用 DDR5(DRAM)时,寄存器时钟驱动器 (RCD) 电压从 1.2 V 降至 1.1 V。命令/地址 (CA) 信号从 SSTL 更改为 PODL,其优点是当引脚停放在高电平状态时不会消耗静态功耗。

3. DDR5 DIMM 全新电源架构

第三个变化,也是一个重要的变化,是电源架构。使用 DDR5 DIMM,电源管理从主板转移到 DIMM 本身。DDR5 DIMM 将在 DIMM 上配备 12V 电源管理 IC (PMIC),从而实现更好的系统电源负载粒度。PMIC分配1.1 V VDD电源,通过更好的DIMM电源控制,帮助提高信号完整性和噪声。

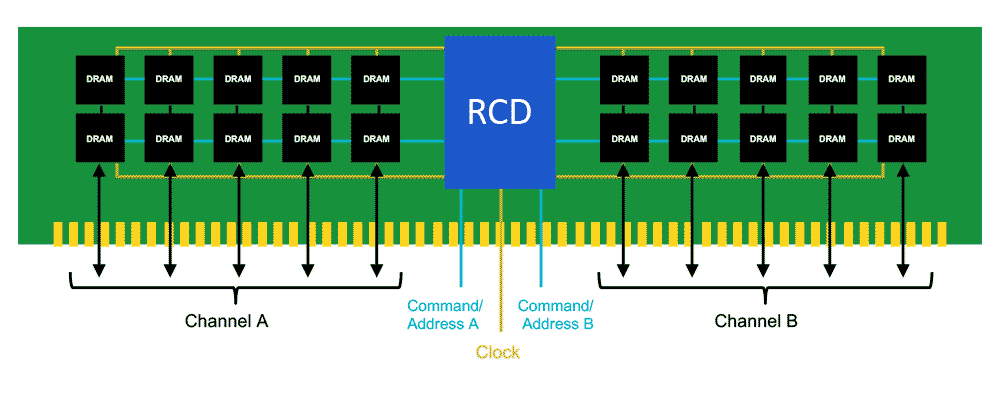

4. DDR5 与 DDR4 通道架构

DDR5 的另一个重大变化是新的 DIMM 通道架构,这是我们列表中的第四位。DDR4 DIMM 具有 72 位总线,由 64 个数据位和 8 个 ECC 位组成。使用 DDR5 时,每个 DIMM 将有两个通道。每个通道的宽度为 40 位:32 个数据位和 8 个 ECC 位。虽然数据宽度相同(总共 64 位),但具有两个较小的独立通道可提高内存访问效率。

在 DDR5 DIMM 体系结构中,DIMM 的左侧和右侧(每个都由一个独立的 40 位宽通道提供服务)共享 RCD。在 DDR4 中,RCD 每侧提供两个输出时钟。在 DDR5 中,RCD 每侧提供四个输出时钟。在具有 x4 DRAM 的最高密度 DIMM 中,这允许每组 5 个 DRAM(单列、半通道)接收自己的独立时钟。为每个列和半通道提供一个独立的时钟可提高信号完整性,有助于解决降低VDD引起的低噪声容限问题(来自上表的变化#2)。

5. 更长的Burst Length

第五个主要变化是Burst Length。DDR4 burst chop length为 4,burst length为 8。对于 DDR5,burst chop length和burst length将扩展到 8 和 16,以增加突发有效载荷。burst length为 16 (BL16),允许单个burst 访问 64 字节的数据,这是典型的 CPU cache line大小。它只能使用两个独立通道中的一个来执行此操作。这显著提高了并发性,并且具有两个通道,具有更高的内存效率。

6. DDR5 支持更高容量的 DRAM

第六个值得强调的变化是 DDR5 对更高容量 DRAM 设备的支持。借助 DDR5 buffer chip DIMMs,服务器或系统设计人员可以在单芯片封装中使用高达 64 Gb 的密度 DRAM。DDR4 采用单芯片封装 (SDP) 的最大容量为 16 Gb DRAM。DDR5 支持片上 ECC、错误透明模式、封装后修复以及读写 CRC 模式等功能,以支持更高容量的 DRAM。更高容量DRAM设备的影响显然会转化为更高容量的 DIMM。因此,虽然 DDR4 DIMM 的容量高达 64 GB(使用 SDP),但基于 DDR5 SDP 的 DIMM 是 DDR5 的四倍,达到 256 GB。

7. 配备 DDR5 的更智能的 DIMM

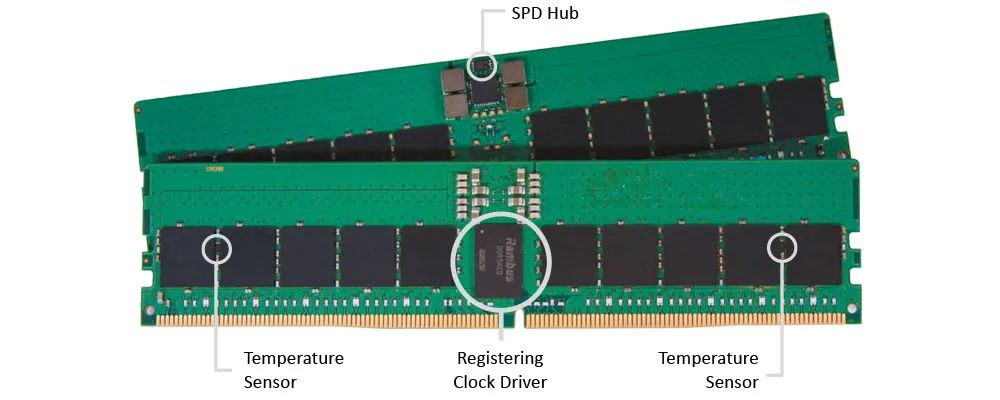

DDR5 服务器 DIMM 芯片组用SPD Hub IC 取代了 DDR4 SPD IC,并增加了两个温度传感器 (TS) IC。SPD Hub具有集成的 TS,它与两个分立的 TS IC 结合使用,提供来自 RDIMM 的三个热遥测点。

借助 DDR5,芯片之间的通信总线升级到 I3C,其运行速度比 DDR4 中使用的 I2C 总线快 10 倍。DDR5 SPD Hub处理从模块到基板管理控制器 (BMC) 的通信。DDR5 SPD 集线器使用更快的 I3C 协议,可缩短初始化时间,并支持更高的轮询率和实时控制。

从 SPD 集线器传送到 BMC 的散热信息可用于管理冷却风扇速度。现在可以更精细地管理 DRAM 刷新率,以提供更高的性能或更高的保留时间,如果 RDIMM 运行过热,可以根据需要限制带宽以降低热负载。

DDR5 的设计挑战是什么

DDR5 的这些变化引入了许多设计考虑因素,以应对更高的速度和更低的电压,从而引发了新一轮的信号完整性挑战。设计人员需要确保主板和 DIMM 能够处理更高的信号速度。在执行系统级仿真时,需要检查所有DRAM位置的信号完整性。

对于 DDR4 设计,主要的信号完整性挑战在于双数据速率 DQ 总线,而对低速命令地址 (CA) 总线的关注较少。对于 DDR5 设计,即使是 CA 总线也需要特别注意信号完整性。在 DDR4 中,考虑使用差分反馈均衡 (DFE) 来改进 DQ 数据通道。但对于 DDR5,RCD 的 CA 总线接收器也需要 DFE 选项,以确保良好的信号接收。

主板上的供电网络 (PDN) 是另一个考虑因素,包括带有 PMIC 的 DIMM。考虑到更高的时钟和数据速率,您需要确保 PDN 能够处理以更高速度运行的负载、良好的信号完整性以及为 DIMM 提供良好的清洁电源。

从主板到 DIMM 的 DIMM 连接器也必须处理新的时钟和数据速率。对于系统设计人员来说,在印刷电路板 (PCB) 周围的时钟速度和数据速率较高的情况下,必须更加重视系统设计的电磁干扰和兼容性(EMI 和 EMC)。

DDR5 内存接口芯片组如何利用 DDR5 for DIMM 的优势

好消息是 DDR5 内存接口芯片提高了从主机内存控制器发送到 DIMM 的命令和地址信号的信号完整性。两个通道中每个通道的总线都流向 RCD,然后扇出到 DIMM 的两半。RCD 有效地减少了主机内存控制器看到的 CA 总线上的负载。

包括 SPD Hub 和 TS 在内的扩展芯片组可实现更智能的 DIMM,它可以在 DDR5 的更高数据速率下运行,同时保持在所需的功率和散热范围内。

Rambus 提供 DDR5 内存接口芯片组,可帮助设计人员充分利用 DDR5 的优势,同时应对更高数据、CA 和时钟速度带来的信号完整性挑战。Rambus 是业内第一家提供 DDR5 RCD 至 5600 MT/s 的公司,并不断提高其 DDR5 解决方案的性能,以满足不断增长的市场需求。Rambus DDR5 RCD 现已达到 7200 MT/s 的性能水平。